Vivado 常见错误及解决策略

安装 & 启动

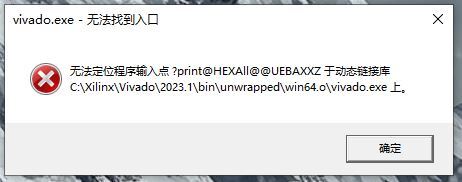

Vivado entry point not found

软件版本

Vivado 2022.1

问题描述

双击 Vivado 后应用程序无法启动,提示 无法定位程序输入点于动态链接库

且提示缺少多个 dll,重装 Vivado 2022.1 或 Vivado 2022.2 后均无法解决问题

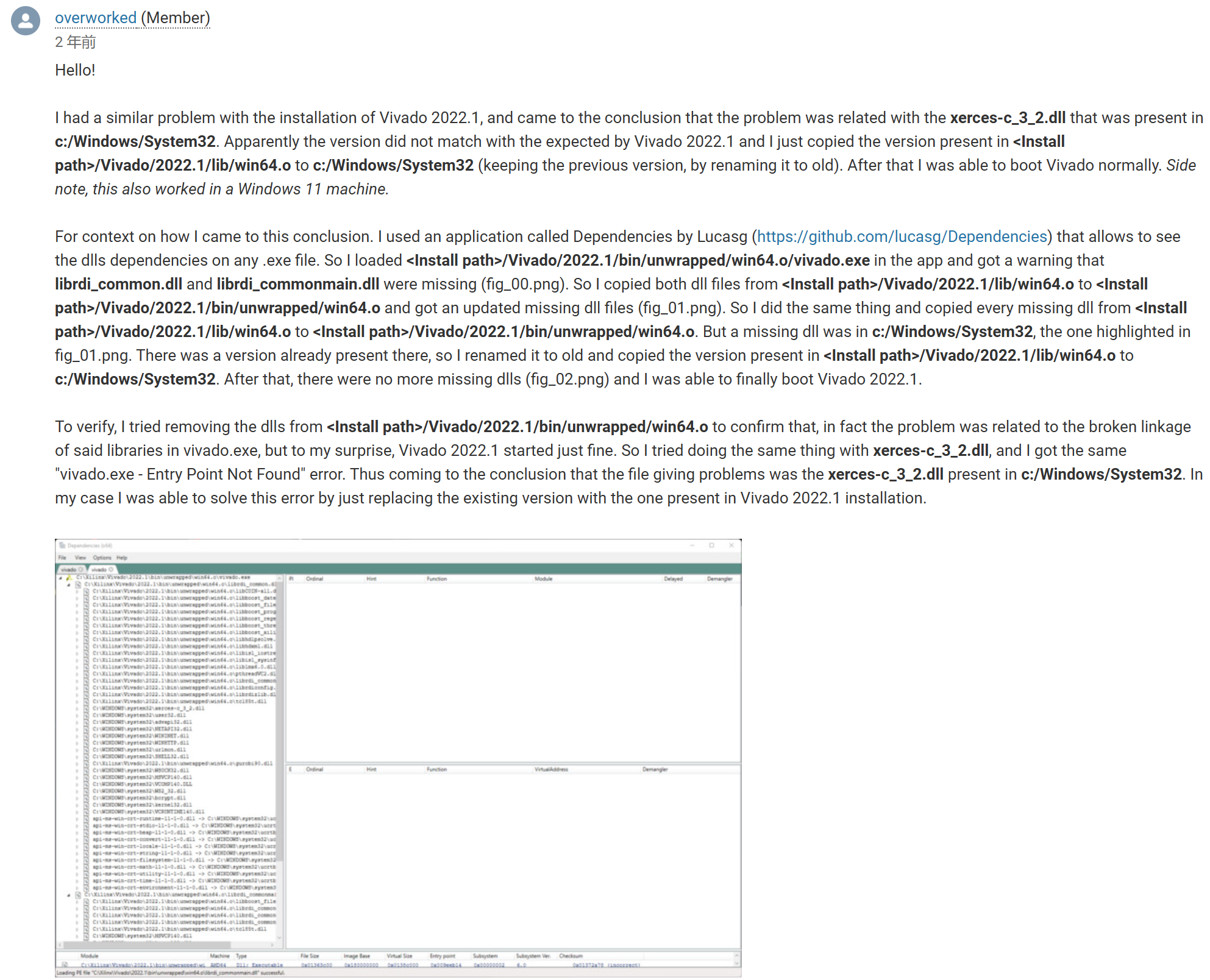

解决方案

出现该问题的原因很多,这里分享 解决笔者问题的方案

将 {install_path}/Vivado/{version}/lib/win64.o 目录下的所有 dll 文件拷贝至 {install_path}/Vivado/{version}/bin/unwrapped/win64.o 文件夹下,即可正常打开 Vivado

install_path:Vivado 安装目录version:Vivado 版本号

布局布线

OPT 31-306

软件版本

Vivado 2022.1

问题描述

在 ZCU106 开发板上使用 DDR4 MIG IP 核时综合通过,布局布线报错

1 | ERROR: [Ip 78-112] Not able to find enough and valid I/O's in the device selected to fit this configuration. Require minimum of 155 enough and valid I/O's. Please choose bigger device to accommodate or modify the memory configuration (for eg. reducing Datawidth or opting for low density memory part etc..) to fit in this device. |

解决方案

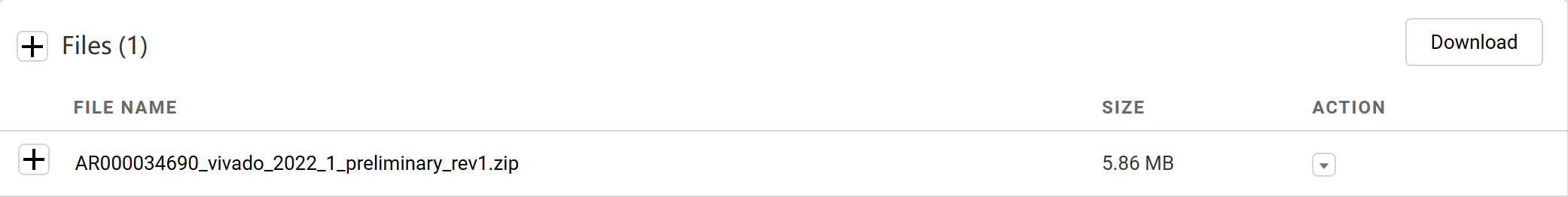

系 Vivado 自身 Bug,解决方案来自 Xilinx 官网论坛,首先下载补丁文件

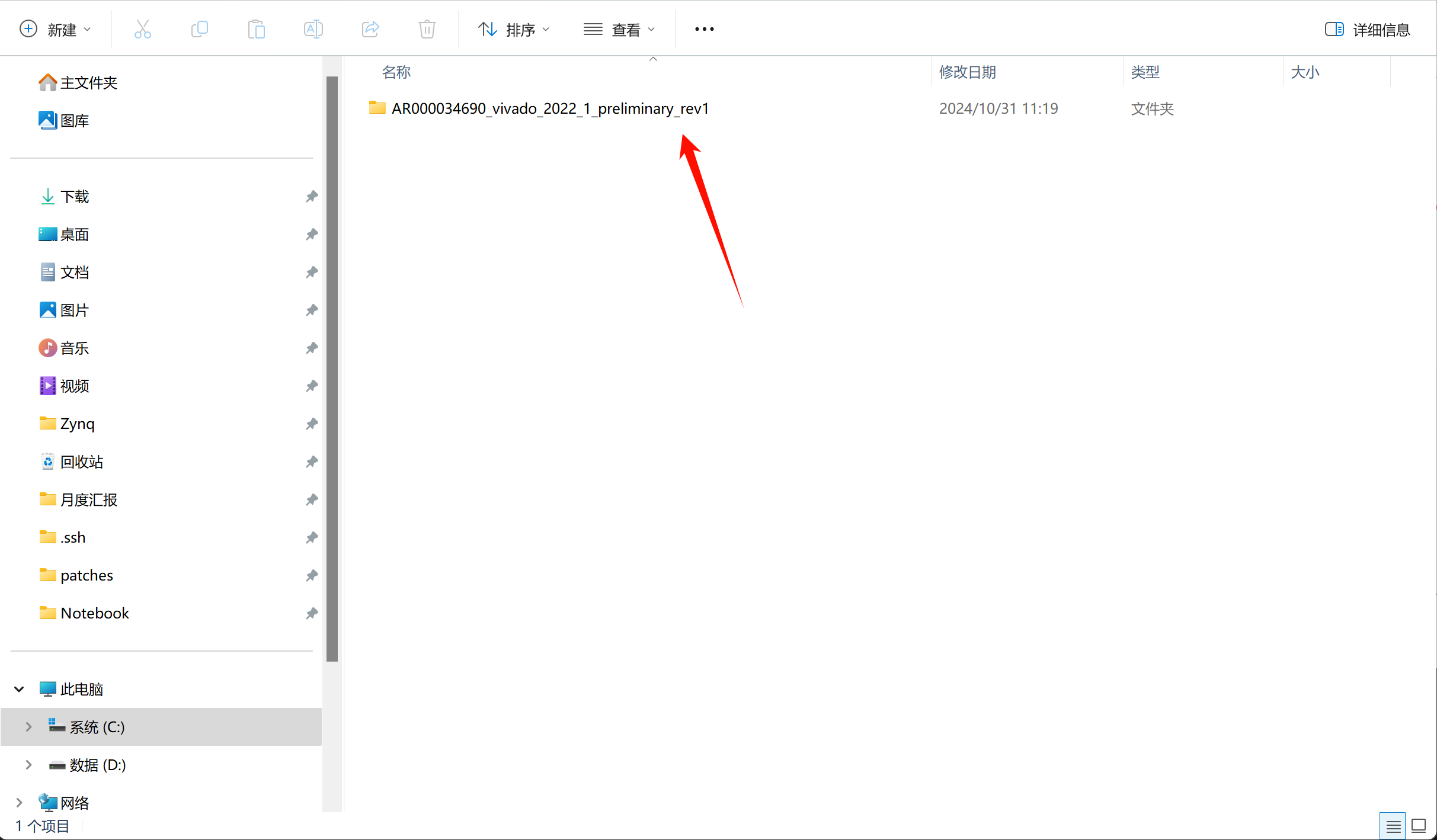

解压后将整个文件夹拷贝至 Vivado 补丁文件夹下,默认 ${install_dir}/${version}/patches(如:C:\Xilinx\Vivado\2022.1\patches),patches 文件夹不存在则手动创建

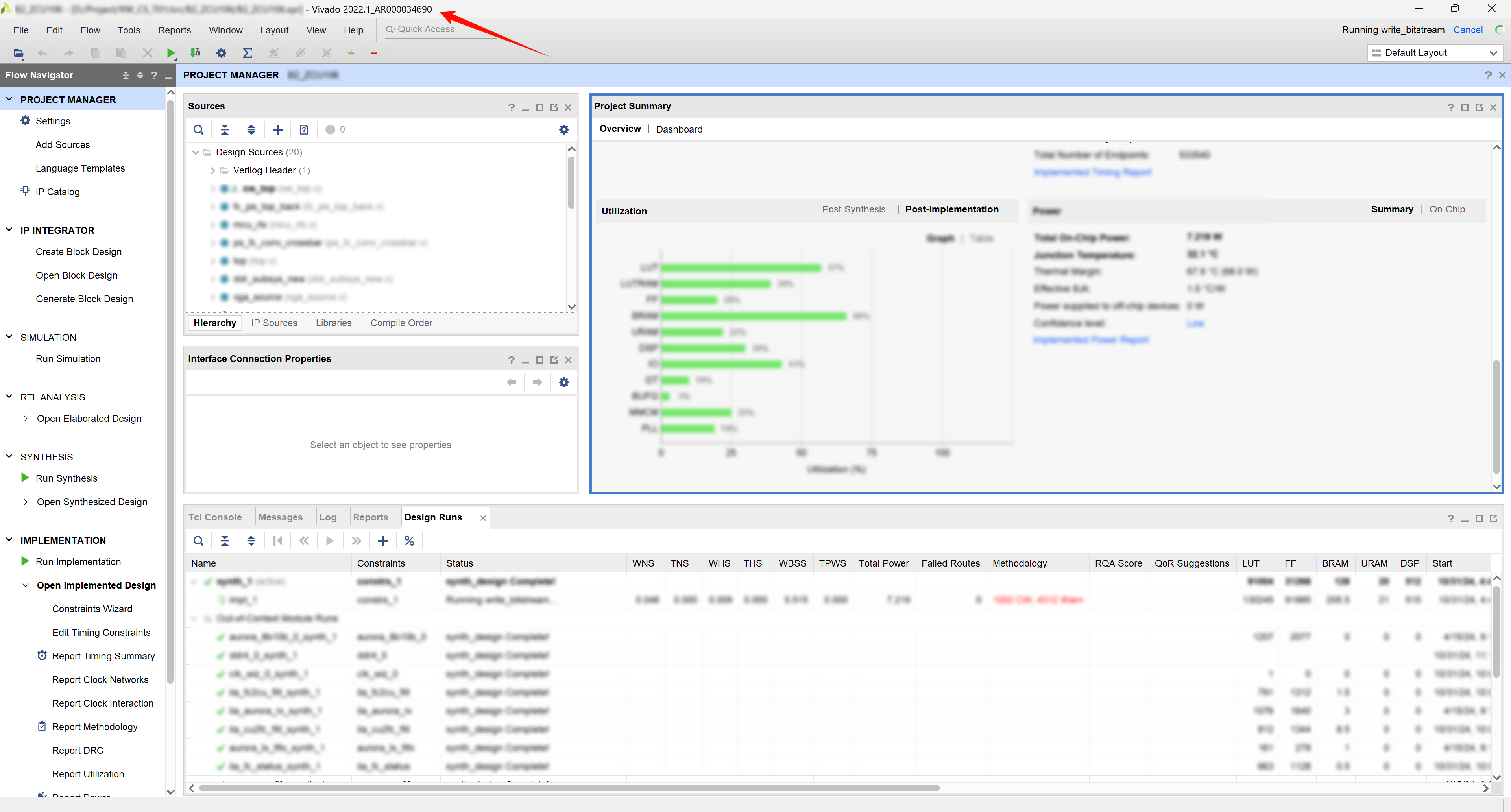

重启 Vivado 后标题栏应显示补丁编号

Stuck at “Initializing design”

软件版本

Vivado 2022.1

问题描述

布局布线时长时间卡在 Initializing design 阶段,Log 终端里 Implementation 始终没有更新,Design Runs 终端 impl_1 的 Elapsed 始终为 00:00:00,多次重启 Vivado 或 Reset/Launch Runs 均无效

解决方案

可能是由于 {project_path}/{project_name.runs}/impl_1/runme.log 文件被其他应用占用,导致 Vivado 无法获取读写权限,结束占用该文件的相关任务即可。参考流程如下

- 检查是否有 VS Code 打开该 runme.log,如果有则关闭相应选项卡

- 任务管理器中搜索 Vivado,查看是否有 Vivado 残余任务,如果有手动结束即可

- 重新进行综合、布局布线

如果上述方案无法解决,同时确定设计无问题、Message 栏无 Critical Warning,可尝试 重启电脑 再综合、布局布线

Block Design

BD 41-758

软件版本

Vivado 2022.1

问题描述

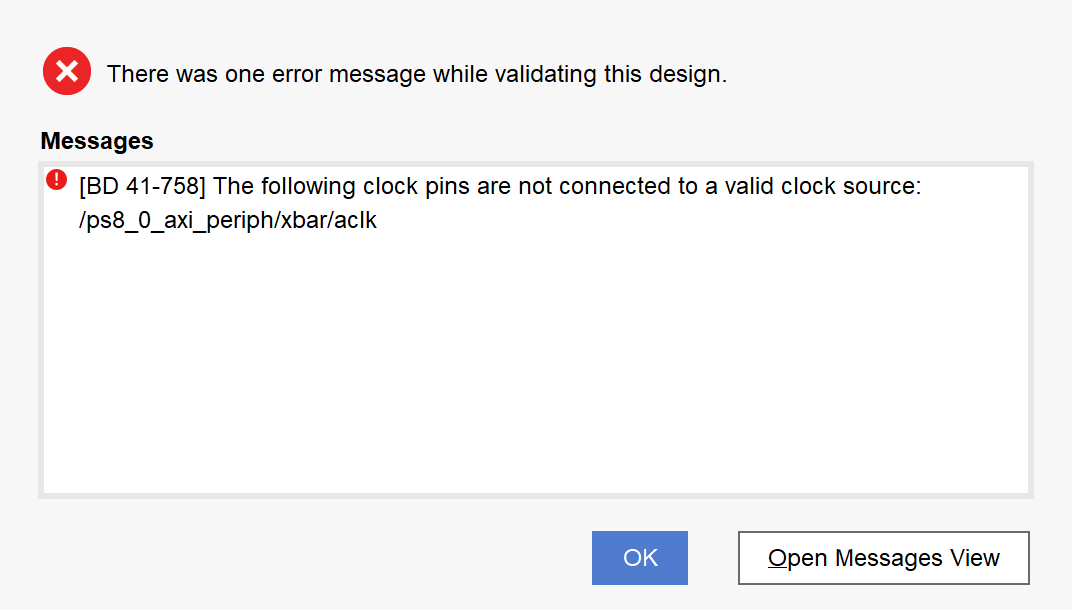

检查 Block Design 设计时提示 The following clock pins are not connected to a valid clock source:/xxx,经检查该端口正常连接时钟源,且此前检查未报错可正常编译,Reset Output Products 无效

解决方案

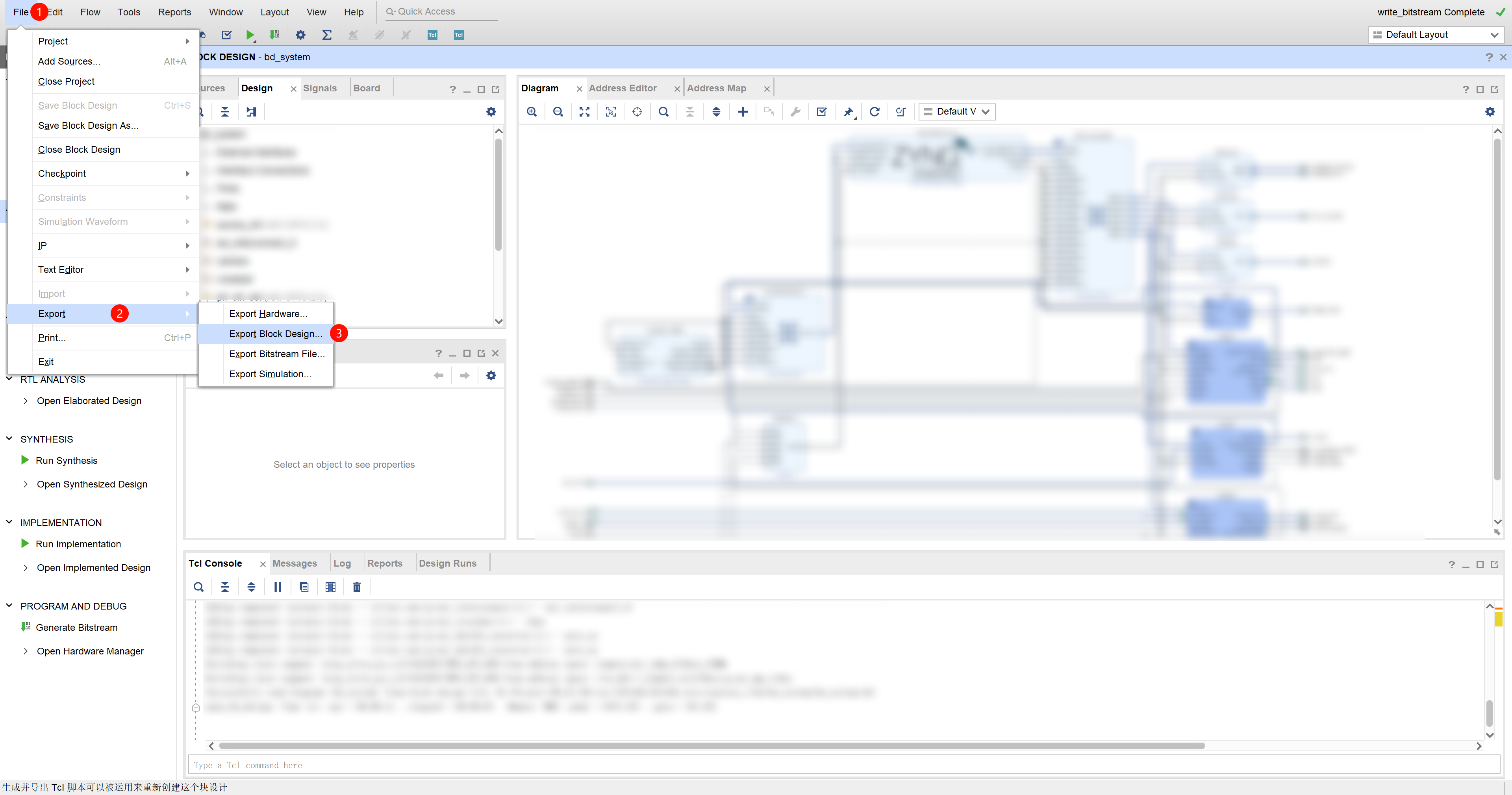

这种一般情况下是 Block Design 抽风了,重建 Block Design 即可。首先点击 File > Export > Export Block Design 导出 Block Design

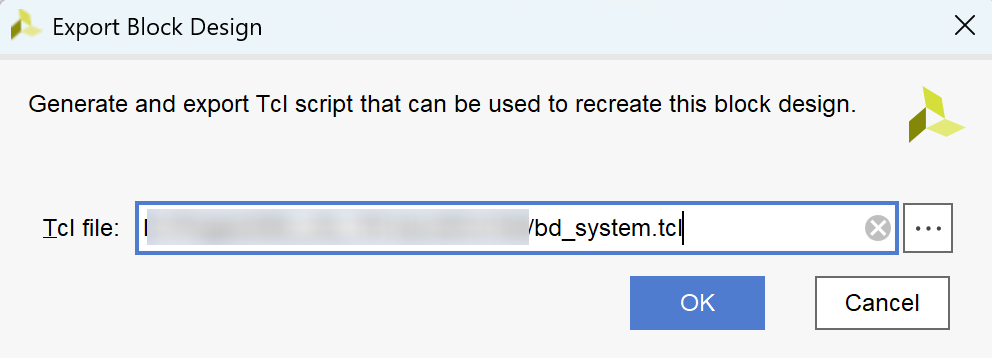

设置 tcl 文件路径,点击 OK

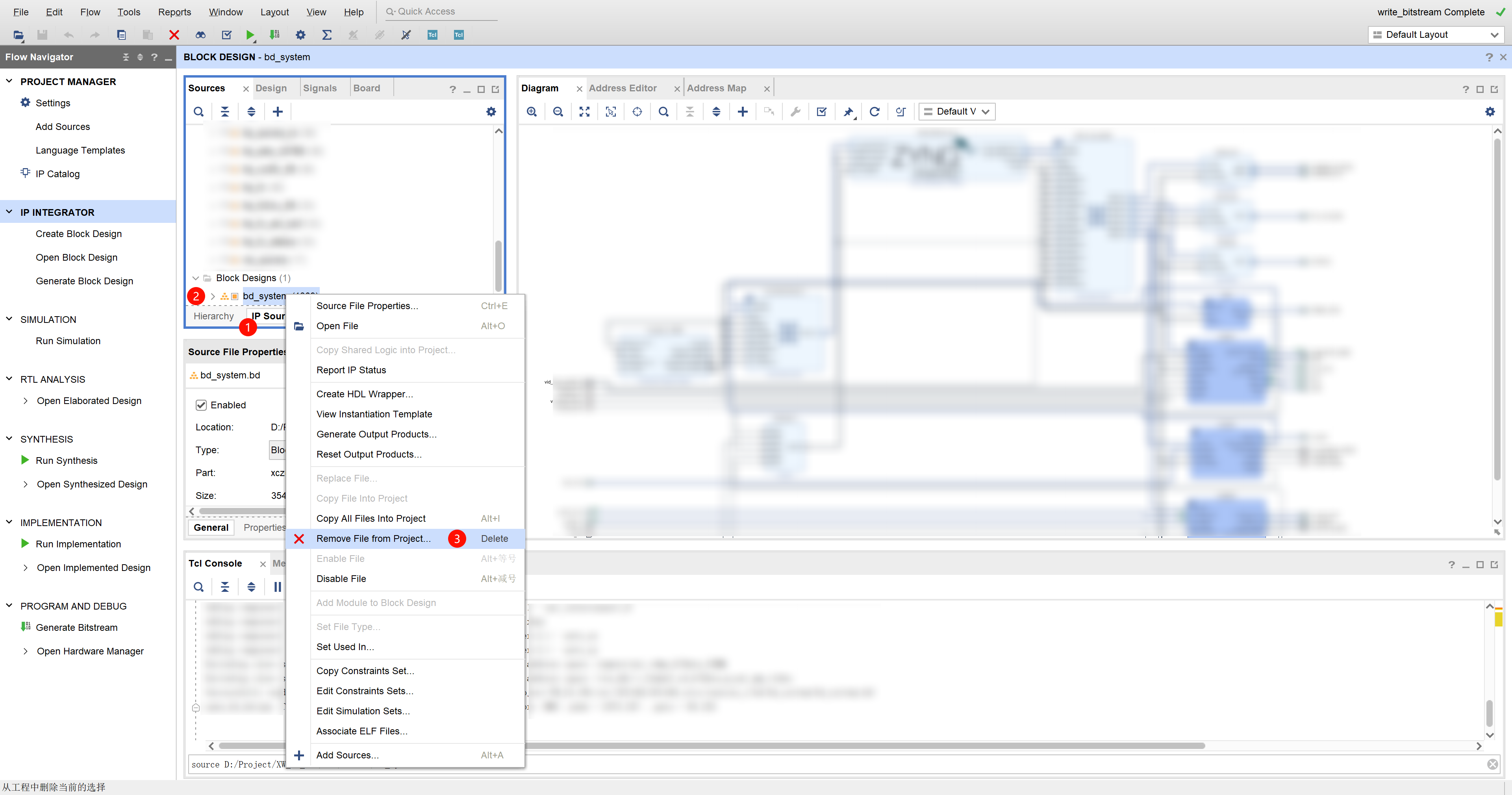

点击 IP Sources,在 Block Designs 中选中有问题的 Block Design,右键 > Remove File from Project,删除现有 Block Design

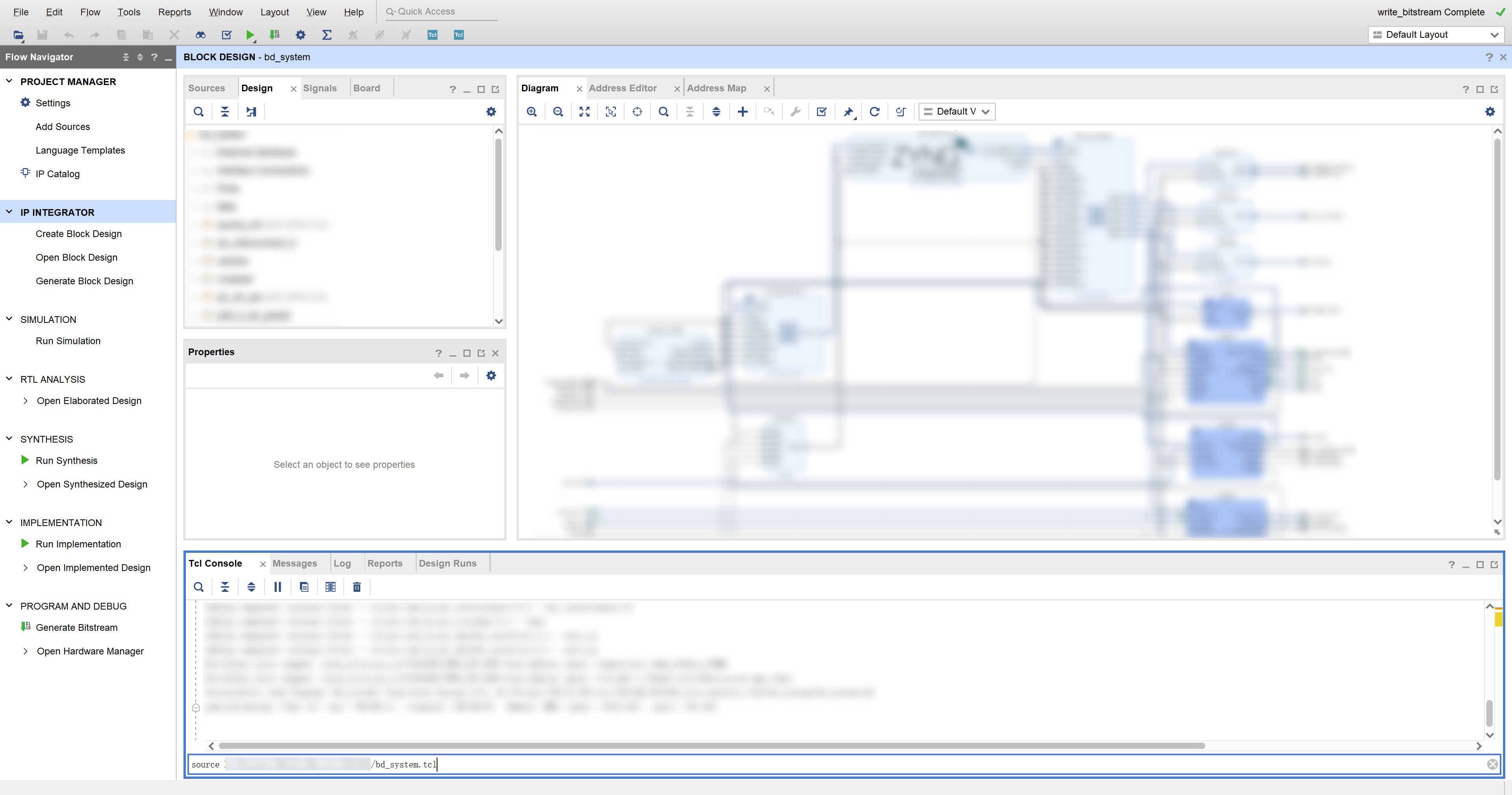

在 Tcl Console 中执行 tcl 脚本重建 Block Design,然后重新 Generate Block Design 即可

1 | source {tcl_directory}/bd_system.tcl |

BD 41-968

软件版本

Vivado 2022.2

问题描述

将设计的 Verilog 模块导入 Block Design 时发生错误

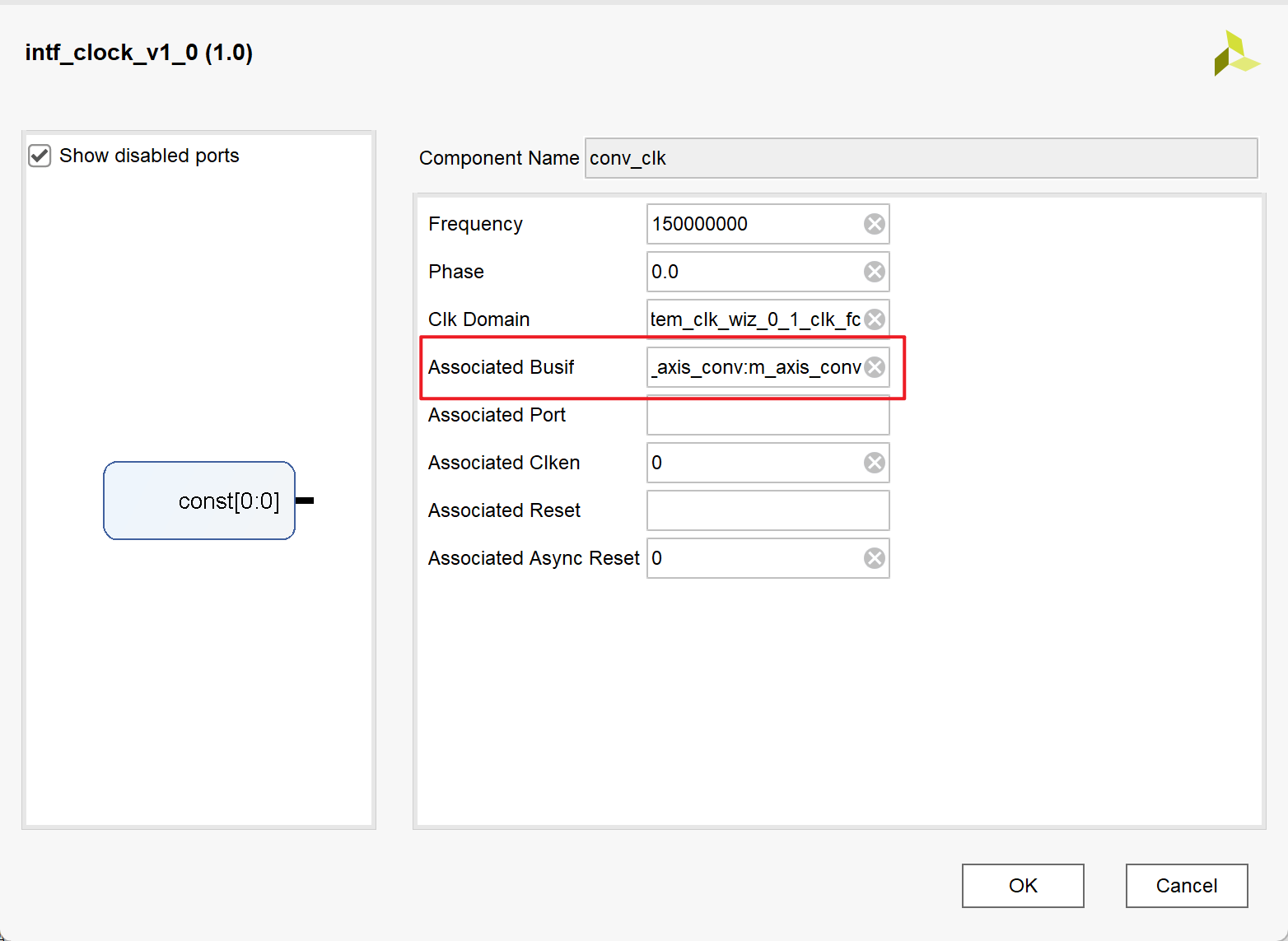

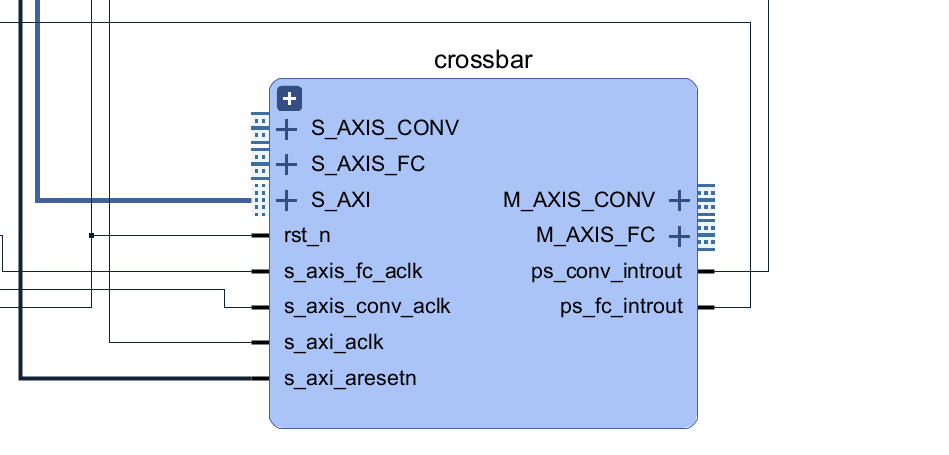

每个 AXI/AXIS 接口都应具有时钟信号,但在设计时不同接口可能共用时钟(如下图中 crossbar 模块的 S_AXIS_CONV 和 M_AXIS_CONV 共用 s_axis_conv_aclk 信号),但 Vivado 无法自动将单个时钟绑定至多个接口

解决方案

双击 s_axis_conv_aclk,在 Associated Busif 中输入 S_AXIS_CONV:M_AXIS_CONV 绑定总线接口即可,多个接口通过 : 分割